Bagaimana hasilnya? Tujuan eksperimen ini untuk membuktikan kalau superhet triple conversion bisa direalisasikan. Jadi layak untuk dicoba. Pada kasus saya, hasilnya tidak sebaik superhet double conversion. Meski modulasi layak didengar, cukup saja nilainya hehe. Mungkin IF xtal saya jelek? Susunan rangkaian kurang pas?

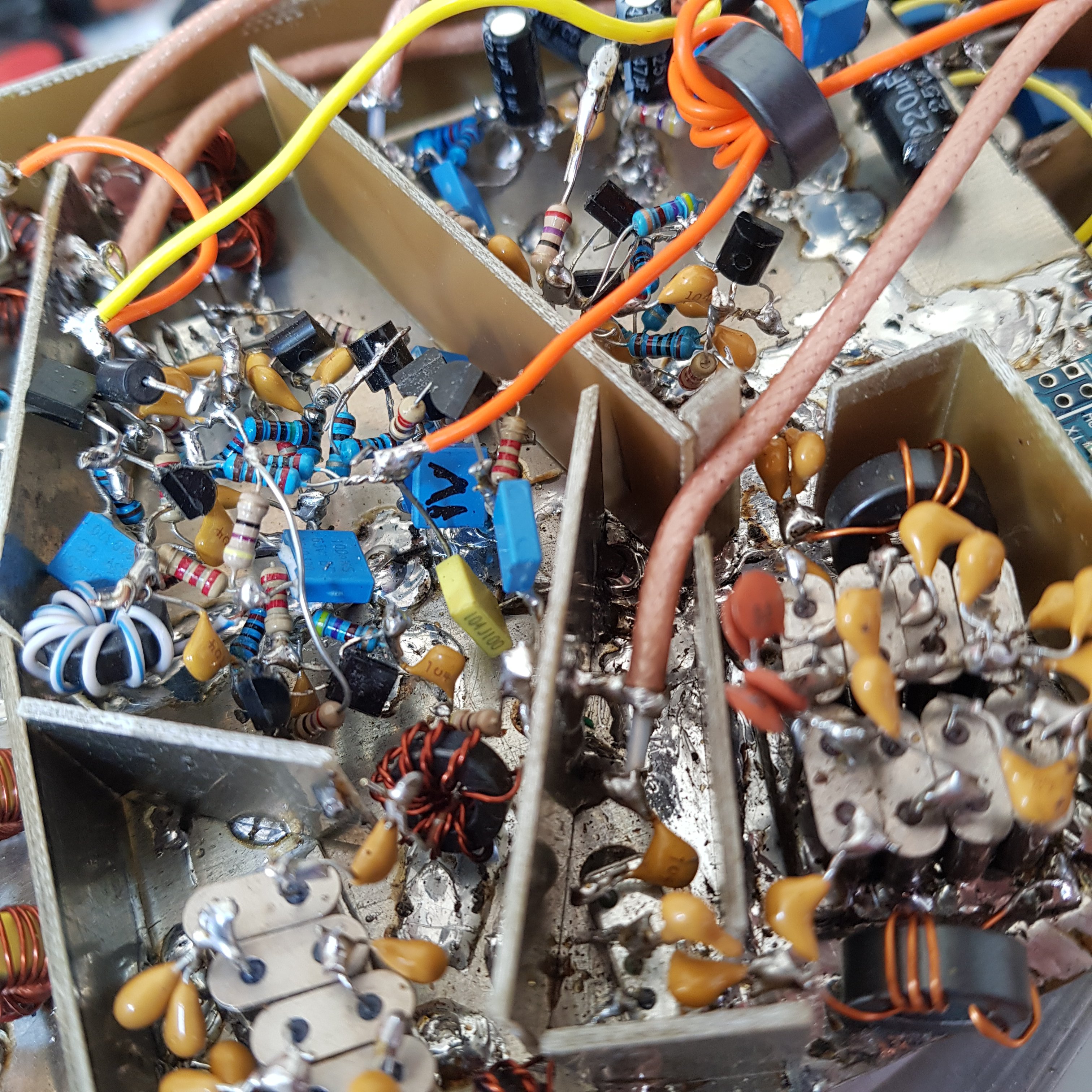

Ujicoba triple conversion ini telah merusak 2 buah mixer TUF-1SM. Jebol karena panas solder berlebih. Saya melakukan kesalahan menyolder body mixer ini untuk grounding. Pengaturan LO & BFO juga berlangsung puluhan kali karena berurusan dengan 3 buah IF (tanpa alat ukur yang valid, Anda tidak tahu bagaimana filter xtal Anda bekerja. Jika angka simulasi mengatakan center frekuensi x MHz, apakah dalam praktek seperti itu?).

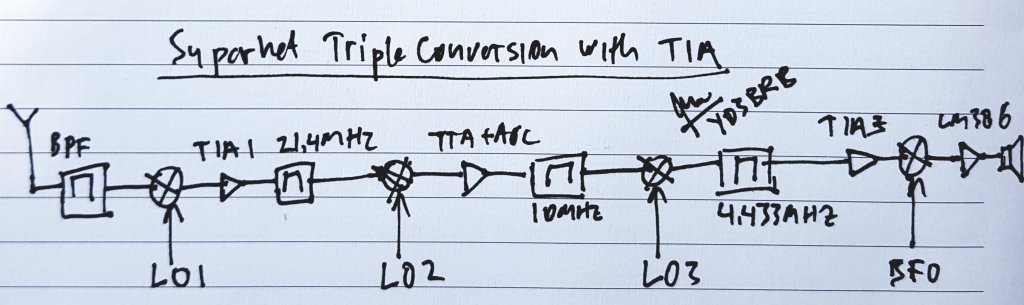

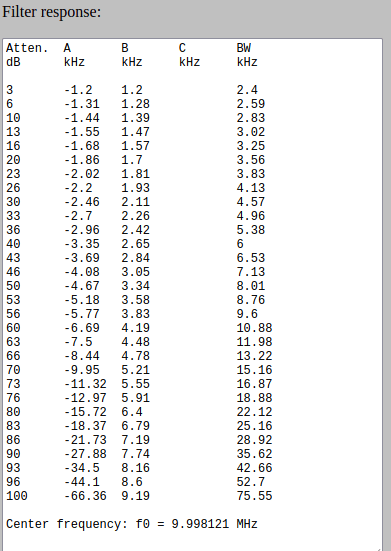

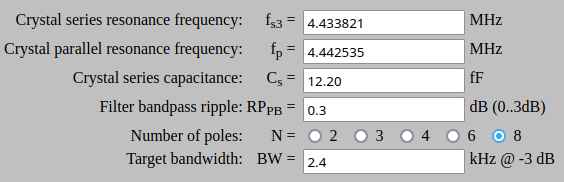

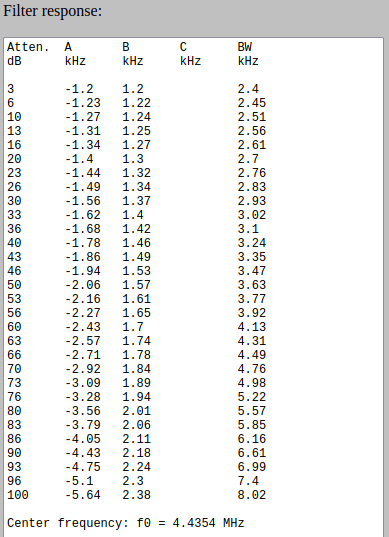

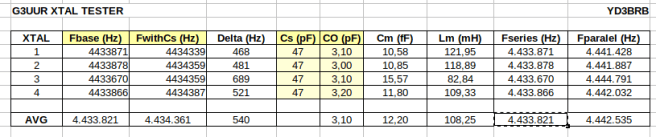

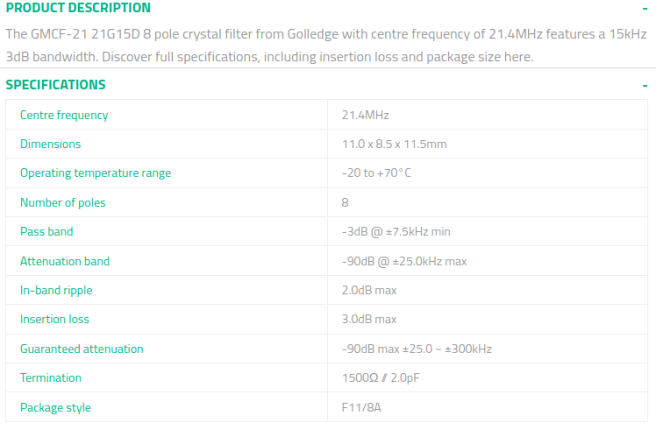

Susunan IF xtal filter sebagai berikut : IF1 = 8 pole xtal 21,4MHz (BW=15KHz), IF2 = 4 pole xtal 10MHz (BW=2,4KHz), dan IF3= 8 pole xtal 4,434MHz ( BW=2,4KHz). Karena eksperimen ini dimulai dari rangkaian double conversion, BW dari IF2 xtal 10MHz saya biarkan sekitar 2,4KHz. Mungkin urutan BW 15KHz sebagai roofing filter, lanjut ke 7KHz, dan terakhir 2,4KHz lebih ideal.

Impedansi IF xtal filter 21,4MHz adalah 1500Ohm, untuk IF2 xtal 10MHz 200Ohm dan IF3 xtal 4,433709 adalah 1500 Ohm atau opsi lain 2150Ohm. Untuk yang terakhir saya menggunakan impedance matching, kombinasi dari L dan C agar match dengan 50Ohm.

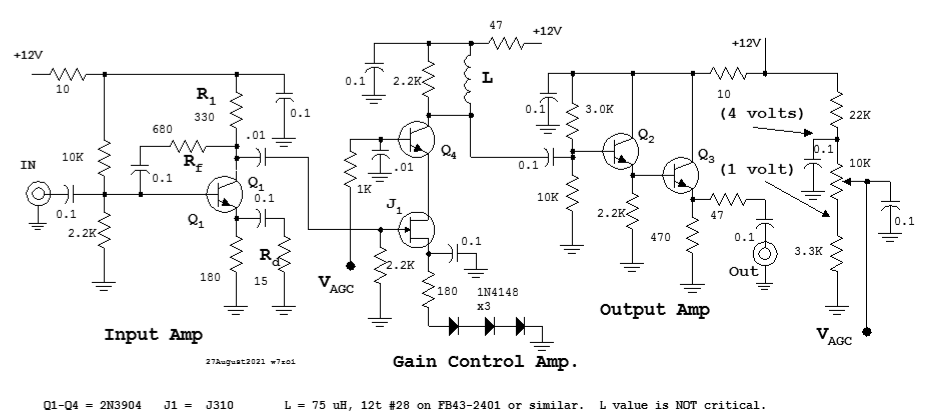

Ada 3 blok TIA yang digunakan. Masing- masing punya gain sebesar 22dB. Untuk blok yang kedua, digunakan TIA+AGC yang pengaturan dilakukan secara manual.

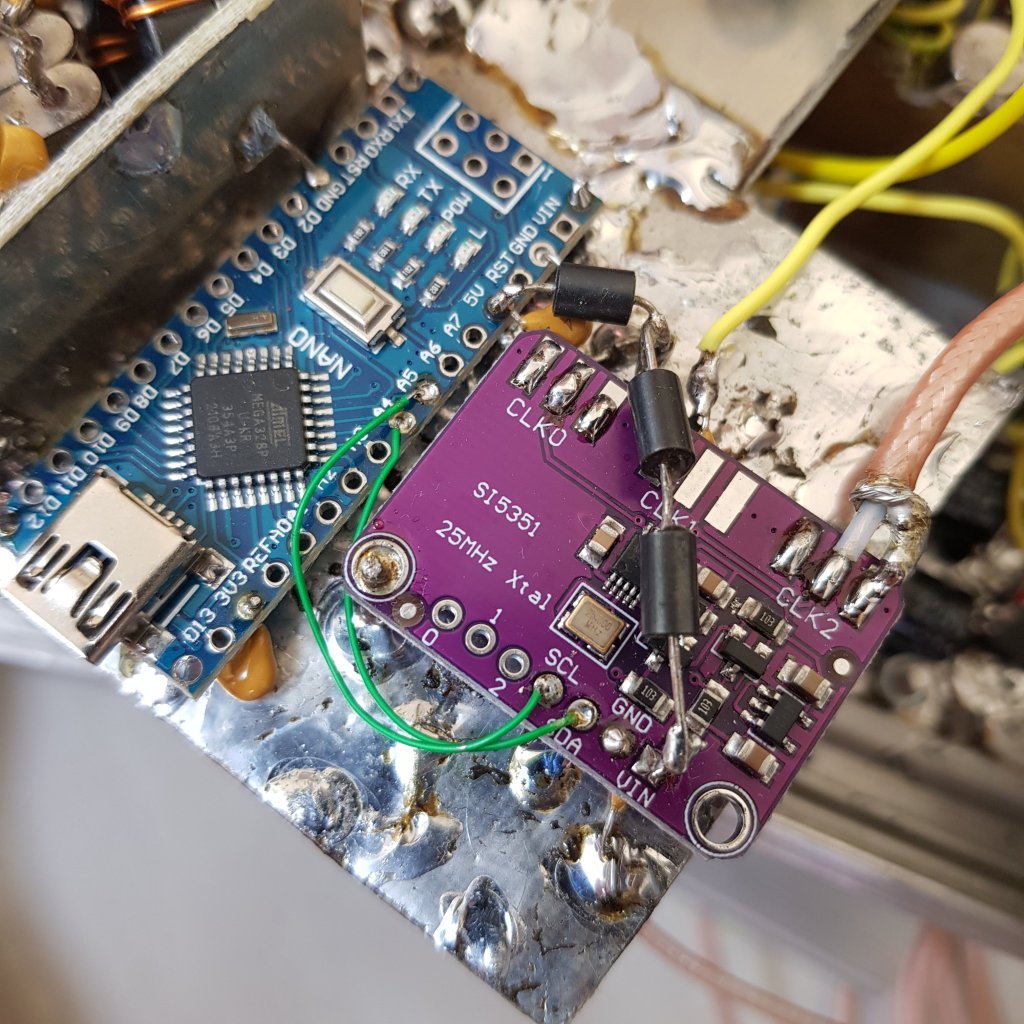

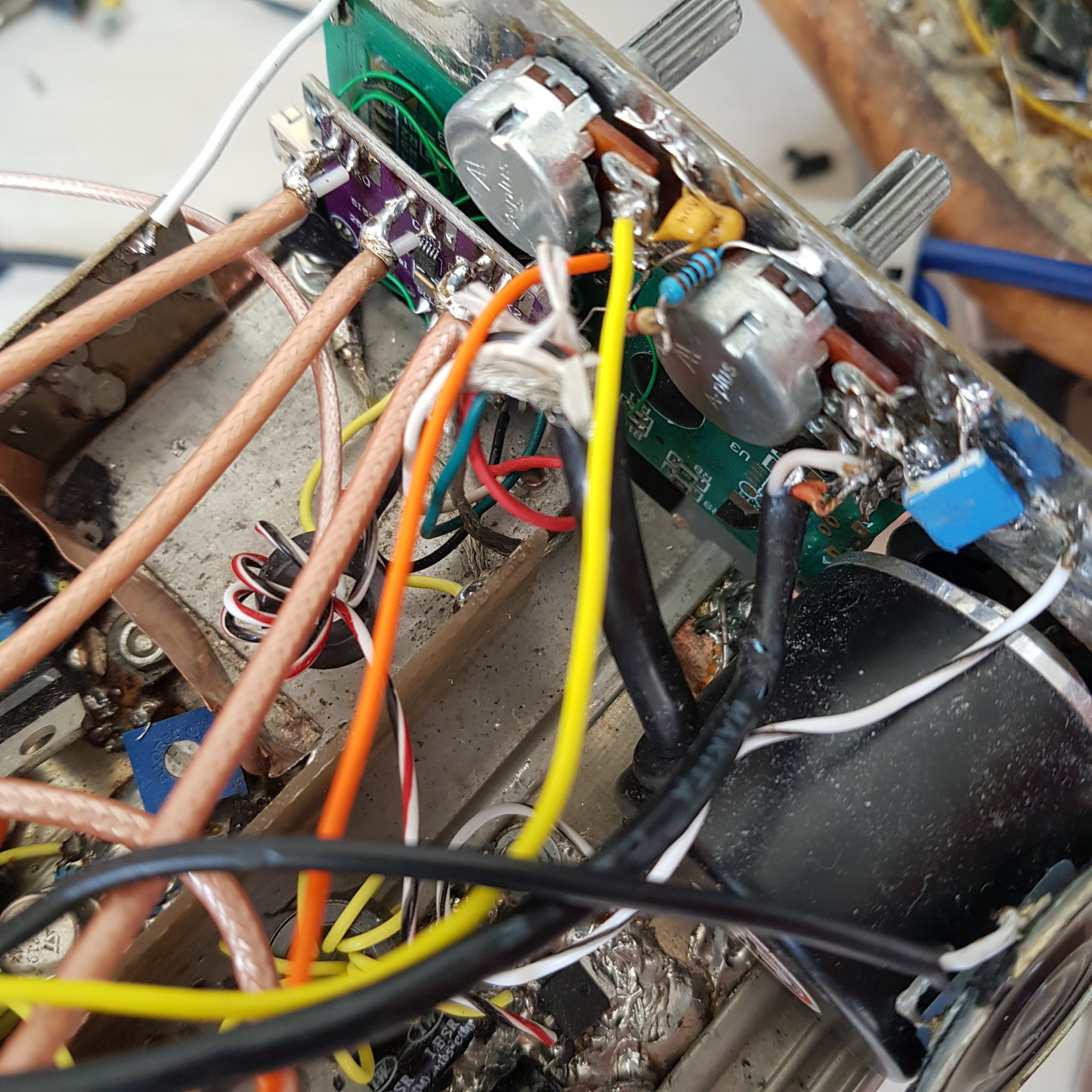

Digunakan 2x Si5351 dan 2x arduino nano. Chip Si5351A dengan tiga output tidak punya pin A0 untuk mengatur Address internal, hingga I2C sebuah arduino Nano tidak bisa mengatur 2x Si5351A ini. Rencana awal untuk BFO saya gunakan rangkaian oscilator standar. Dalam prakteknya, menggeser frekuensi kerja xtal 4,43MHz tidak semudah xtal 10MHz. Saya hanya mampu menggeser 700Hz saja dari center frekuensi. Sedang saya butuh sampai 1,5KHz. Terpaksa saya gunakan tambahan Si5351A khusus BFO.

Sedangkan mencari celah agar salah satu LO bisa diganti rangkaian oscilator juga kerepotan karena diperlukan xtal dengan nilai yang tidak ada dipasaran. Menggeser terlalu jauh nilai frekuensi dari nilai xtal akan menyebabkan ketidakstabilan.

Ada 4 buah output clock yang dibutuhkan. (Perhitungan di bawah ini kasus saya yach… bisa jadi gak cocok dengan kasus Anda. Tapi “garis besar” frekuensi pasti benar, hanya geser sedikit ke atas atau bawah saja). Hasil perhitungan ini setelah mencoba berbagai kombinasi. Tergantung rancangan IF filter tiap perangkat. Perhitungan output clock sebagai berikut :

LO1 = IF1-FTarget, LO2=IF1-IF2, LO3=IF2-IF3, dan BFO=IF3.

Aneh ya, tidak ada minus Bandwidth pada BFO. Mau dijumlah pun hasilnya kacau. Tapi itu yang terjadi untuk LSB. Setelah mengamati hasil simulasi, ternyata center frekuensi dari xtal 4,433MHz bergeser ke atas sebesar 2KHz, jadi sekitar 4,435MHz. Apakah realita seperti itu? Saya tidak tahu juga karena tidak melihat grafik dari sebuah VNA. Patokan saya, modulasi Audio layak didengar. Dan susunan output frekuensi dengan perhitungan di atas adalah terbaik.

Dibanding superhet double conversion, eksperimen superhet triple conversion perlu dirancang lebih detil dan hati-hati. Jika ada “sampah” signal didepan, maka sampah ini akan berlipat dan kececeran dimana-mana karena tiap mixer akan membangkitkan sampah lain. Proses ini terjadi 3x-4x hehehe.

Eksperimen ini tidak dianjurkan untuk pemula yang baru mulai merakit sendiri radionya. Rasa frustasi karena masalah di sana-sini (yang tidak perlu) tidak akan terjadi pada superhet single conversion.

Semoga berguna!

YD3BRB

———————————-

Lampiran :

Data pengukuran xtal, xtal ladder calculator, mixer, dan blok TIA saya lampirkan sekalian sebagai dokumentasi.

https://www.giangrandi.org/electronics/crystalfilters/xtalladder.html

https://www.golledge.com/products/gmcf-21-21g15d/c-26/p-2499

syaa pikir apakah programmable clock SI5351 bisa menghasilkan performance receiver sebanduing VFO ?, karena output Si5351 kan persegi sehingga banya harmonik nya

Sorry baru balas. Ada pro kontra soal ini. Coba cek https://www.markimicrowave.com/engineering/resources/rf-microwave-qa/q/what-is-a-square-wave-lo-driver-amplifier-and-when-should-i-use-it